今年 3 月,英特尔联合创始人、摩尔定律提出者戈登·摩尔在夏威夷家中离世,享年 94 岁。但在戈登·摩尔身后,围绕摩尔定律的争论始终没有落下。英伟达 CEO 黄仁勋在 RTX 40 系显卡发布后针对涨价一事回应时,公开表示「摩尔定律已死」。然而,老对手 AMD CEO 苏姿丰并不认同。

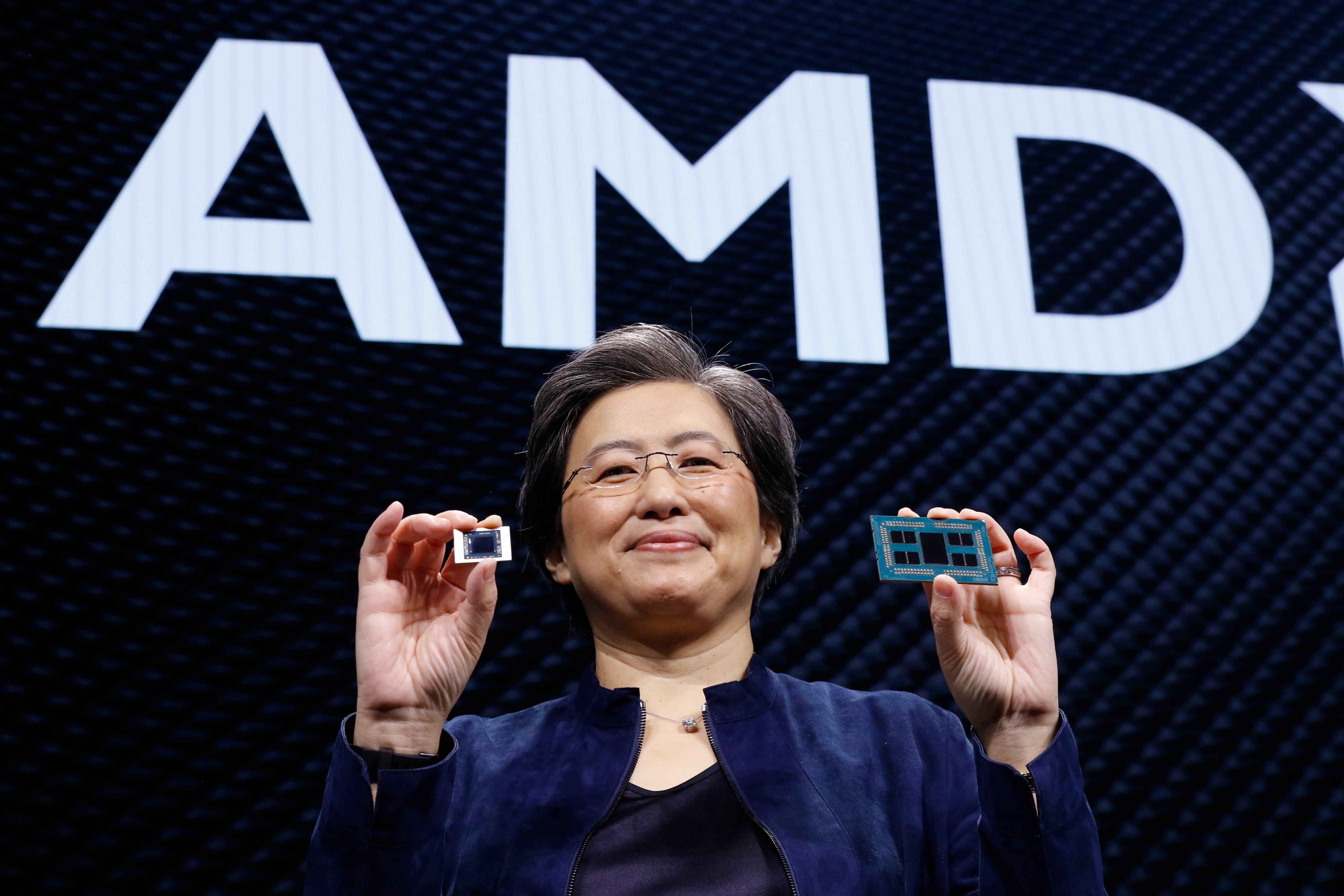

在最近接受《巴伦周刊》的采访中,苏姿丰明确地表示,摩尔定律并未消亡,只是有所放缓,需要采取不同的方式来克服性能、效率和成本上的挑战。她还提到:

「晶体管成本的增加、密度提高带来的改进,每一代的综合性能提升可能都不大,但我们通过不断地更迭,一步一步地向前迈进。我们今天在 3nm 方面做了很多工作,也在研究 2nm,将继续使用 Chiplet 这类结构来试着绕过摩尔定律的一些挑战。」

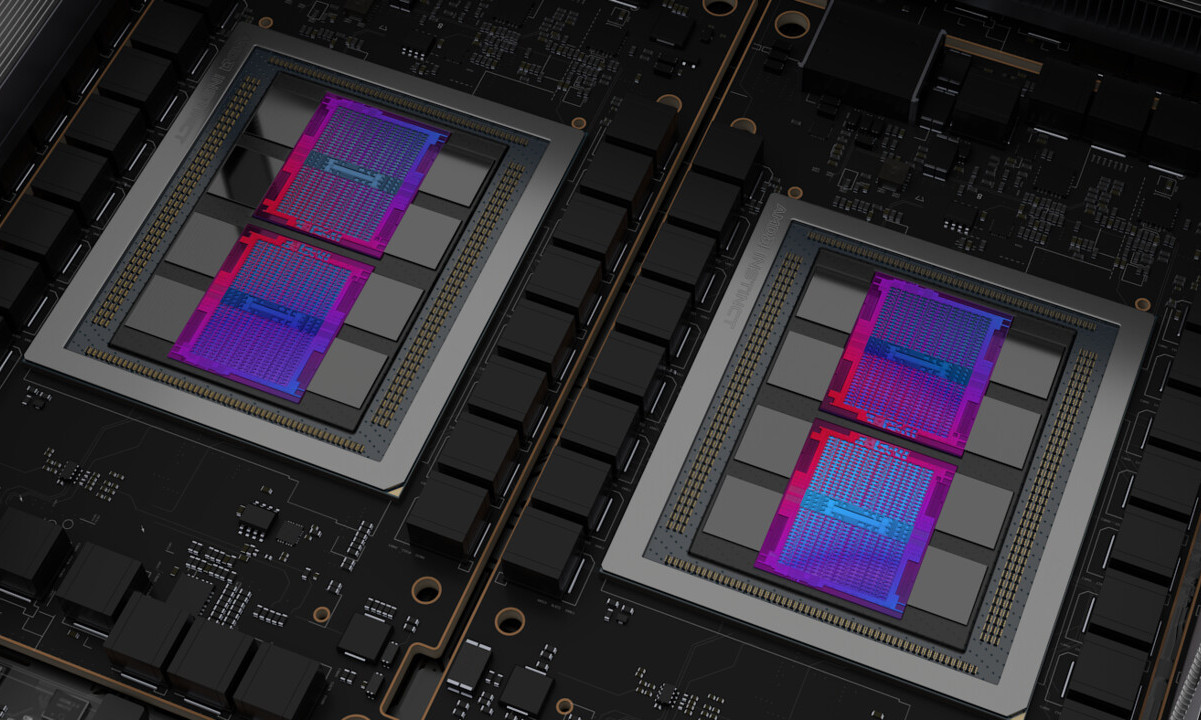

图/AMD

AMD 一直是推进 3D Chiplet 技术的先驱,2017 年就首次在处理器上采用了 Chiplet 技术——将 4 个 SoC 互相连接;2022 年还推出了 RDNA3 架构的 7000 系显卡,这也是史上第一款采用 Chiple 技术的 GPU。

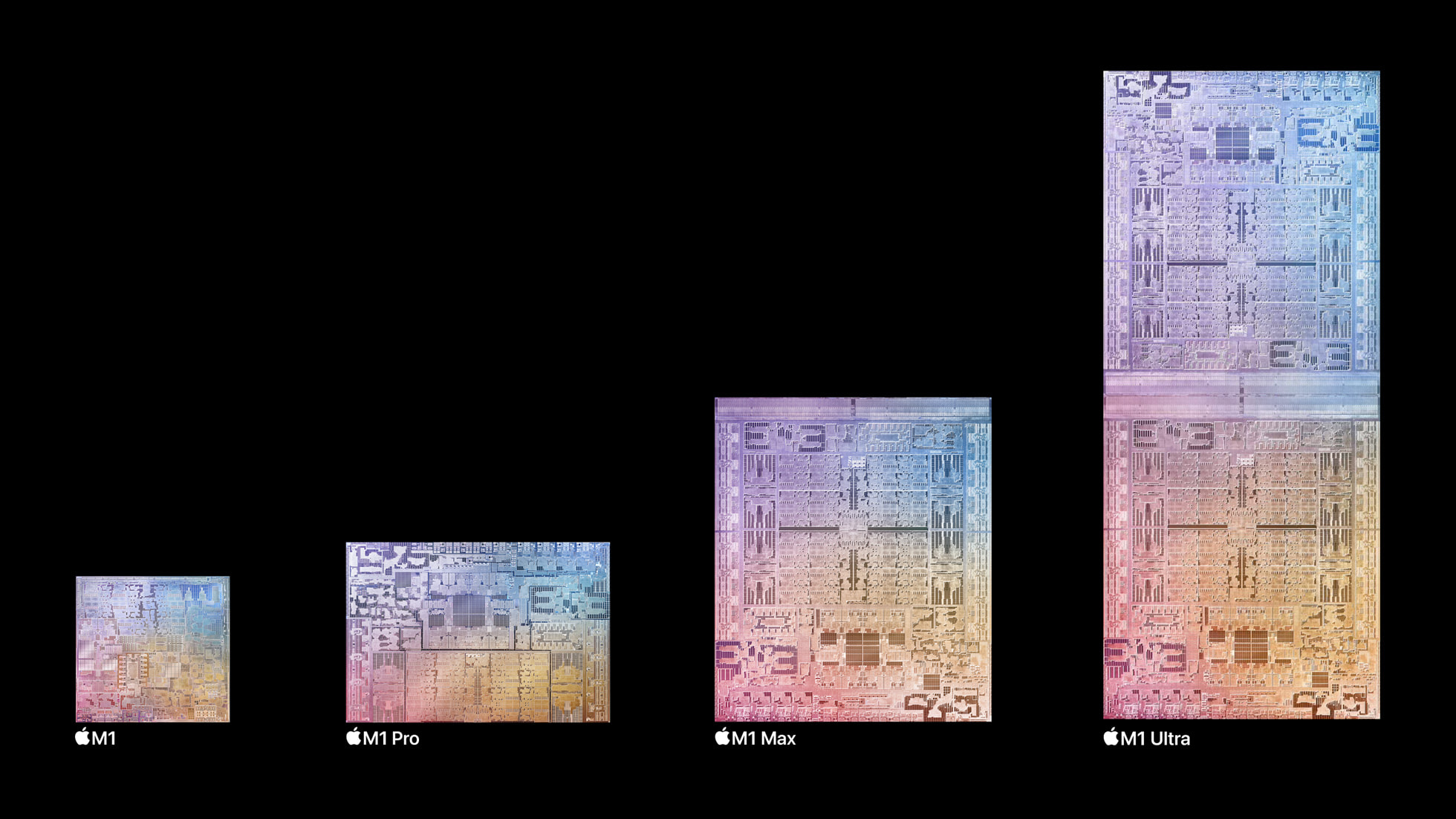

但英特尔和台积电对接下来摩尔定律的发展还要更有信心。英特尔 CEO 帕特·基辛格和台积电高层都认为,摩尔定律不但没有死,也没有放缓,甚至还将在未来 10~20 年以更快的速度驱动芯片性能的提升以及半导体产业的成长。基辛格甚至预测,到 2030 年芯片容纳的晶体管数量将达到 1 兆个——「性能怪兽」苹果 M1 Ultra 容纳的晶体管数量也不过 1140 亿个。而与 AMD 一样,英特尔和台积电也将 Chiplet 技术视为「拯救」摩尔定律的关键救星。

事实上,M1 Ultra 也是在 Chiplet 路线上的产物,其采用的 UltraFusion 架构基于台积电第五代 CoWoS Chiplet 技术的互连架构。

所以在 1nm 及以下工艺并不明朗的当下,Chiplet 就是未来了吗?

图/苹果

小芯片互连,为摩尔定律续命

Chiplet,又称「小芯片」。不同于设计和制造一颗大的 SoC,Chiplet 的设计理念是化繁为简,将原本需要一颗大芯片完成的功能,切分到不同的小芯片上,然后将这些小芯片通过互连技术连接起来,再封装成一个 SoC,就像积木。

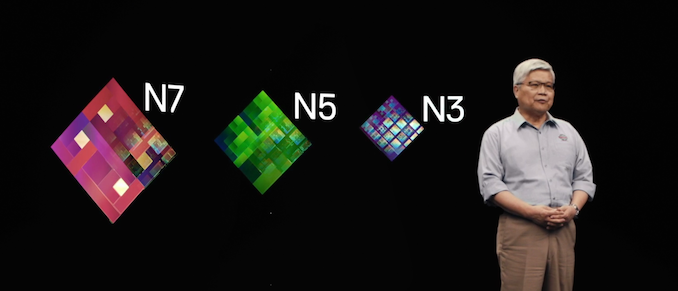

图/APEC

前 Marvell CEO 周秀文最早提出了 Chiplet 的概念,当时他的想法是将很多客户共同使用的 IP 集中在一个小芯片上,有需要时直接加上这颗小芯片,由此可以大幅削减设计和生产成本。不过 Chiplet 真正被产业界关注绕不开摩尔定律。

这条由戈登·摩尔在 1965 年提出的定律认为,集成电路上可容纳的元器件数量每 18 个月便会增加一倍,后在 1975 年又修订为单位面积芯片上的晶体管数量每 24 个月翻一番,意味着芯片性能提高一倍。然而在主导计算世界 50 多年后,芯片工艺升级幅度的放缓以及成本的大幅提升,都让摩尔定律走到了「to be, or not to be」(生存还是毁灭)的十字路口。

按照 Semianalysis 之前的测算,台积电 3nm 测试芯片相比 5nm 在晶体管密度上只提高了 56%,但同时成本却增加了 40%左右,单个晶体管的成本只降低了约 11%,几乎是摩尔定律提出以来主要工艺技术的最弱扩展。这也是为什么目前为止 3nm 客户中,仅有苹果一家有了较为明确的时间表。

台积电先进工艺,图/台积电

同时这也在另一个角度上佐证了,摩尔定律如果只是继续依靠「尺寸微缩」路线从经济上已经难以为继,单个芯片上集成更多的晶体管虽然从技术上来说依然可行,但成本已经大到无法接受,其中先进制程的良率问题是让流片成本居高不下的主要因素之一。

通常来说,芯片的尺寸大致决定了芯片的成本,越大的芯片虽然能容纳的晶体管更多,但成本也越高。一方面是越大的芯片对晶圆的利用率越低,边缘的边角料会剩下更多;另一方面也是因为每一颗大芯片在制造过程中出现问题的概率都更大,导致良率更低,而且尺寸越大出错的概率越高,也意味着成本的成倍增加。

换句话说,当芯片制程已经微缩到接近物理极限,芯片的性能和成本很难按照摩尔定律继续演进,除非我们能用 Chiplet 大幅提高良率,让成熟的 IP 更容易复用,再加上先进的 3D/2.5D 封装,才可能让摩尔定律保持过去的速度,甚至更快。

Chiplet 走到台前,是一种必然

上周,英特尔全球营销总监 Bernard Fernandes 在个人推特上透露,今年下半年即将推出的「Meteor Lake」第 14 代酷睿处理器,将会改用全新的 Core Ultra 命名方式。但不管是不是 Core Ultra,英特尔显然对这款首次采用 Chiplet 小芯片设计的处理器充满了期待。

不仅是英特尔,包括 AMD、华为、苹果、特斯拉、台积电在内的多家芯片公司都表明或已经在产品中导入 Chiplet 设计。AMD 今年 3 月推出了基于台积电 3D Chiplet 封装技术的第三代服务器处理芯片,苹果也推出了采用台积电 CoWos-S 桥接工艺的 M1 Ultra 芯片,此外还有索尼的 CIS、Lightmatter 等。

图/OpenAI

而随着全球范围内 AI 模型的兴起,更多、更大的 AI 模型有了对算力和芯片更高的需求,能否提供更高的算力和更低的成本,势必会成为这场技术浪潮中芯片市场竞争的关键。另一方面,当下超大规模数据中心厂商、自动驾驶厂商、互联网巨头等都在设计自己的芯片,相比更通用的 CPU 和 GPU 厂商,由于无法从出货量上进行分摊,成本就变得更加关键。

另外据 EDA 巨头 Synopsys 的调查报告,目前 Chiplet 技术主要还是应用于服务器和 AI 领域,此外还有网卡/交换机,智能手机/图形/PC 上的一些专用芯片,再就是一些光电共封和汽车领域。而从工艺制程来看,相对先进又成熟的 5nm 工艺在应用 Chiplet 技术上的比例最大,再就是 7nm 和 3nm。

可以预见的是,随着 2.5D、3D 这样先进封装技术的进步,Chiplet 实现一个芯片互连的世界变得越来越成为可能。而在先进制程上对 Chiplet 的应用,至少也说明了我们这个世界依然在追求更强的处理速度和更低的处理成本,前者意味着更高的效率,后者则意味着更高的效率能否普及到更多地方和更多人的生活。

题图为 Instinct MI300,来自 AMD

雷科技

雷科技